OPERATION

MANUAL

FOR

ELECTRONIC

FEATHER TOUCH

KEY

Courtesy of the N7CFO archives. WWW.N7CFO.COM

## INTRODUCTION

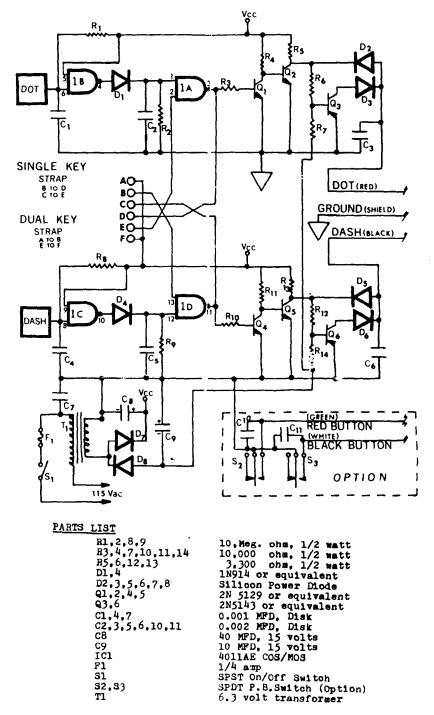

The Electronic Feather Touch K3y is completely solid state. It has been designed to drive the most demanding electronic keyers by the mere touch of fingers to the paidles. Output transistor drivers are provided for keying keyers which operate with negative or positive voltage grounds. Two identical circuits are provided, one comprising the electronics for the D01 paddle, the other for the DASH paddle. Strappable connections between the D0T and DASH electronics are provided to allow the key to function as a Single Paddle or Dual Paddle key. Each circuit consists of two high input impedence COS-MOS NAND gates with associated NPN and PNP transistor. The COS-MOS NAND gates are used to convert the mechanical touch of a finger to a suitable electrical signal for the output transistor drivers. The output drivers are designed to directly drive the input circuitry of any digital keyer using positive or negative voltage grounds.

TWIN KEY OPERATION of the unit will be discussed covering only one of the identical paddle assemblies. The imput to Pin 6 of GlB under static condition is from a high resistance voltage source, El to Vcc. The output, Pin 4, of GlB thus is a O. GlA has a high resistance O on Pin 1 through R2 to ground. Pin 2 of GlA is a 1 from the DUAL KEY strapping, terminal E to F. Pin 3 is a 1 and causes transistor Q1 to conduct placing a O at the base of Q2, not allowing Q2 to conduct. When Q2 is not conducting the voltage divider of R5, 6, 7 establishes a positive voltage at the base of Q3, not allowing Q3 to conduct. When a finger mouches the DOT paddle two conditions may occur. One is that GlB istablishes a steady 1 on its output, Pin 4. This will be the case if a good finger ground touches the DOT paddle. A good finger ground will normally result, however, it can be improved upon by allowing the body or keying hand to physically touch an m3 ground such as the case of the key or keyer. Second 1s that Fin 4 of GlB pulser at a 60 Hertz rate. This will be the case if the finger has a high visione in the total C ground. That is GlB responding to the AC voltage appearing in the operating hand. In case mumber one, the steady 1 on Pin 4 of GlB will pass through Dl onto Pin 1 of GlA. This 1 will force Pin 3 of GlA to a steady 0. In case mumber two, the 1 pulses at Pin 4 of GlB will pass through Dl onto Pin 1 of GlA, via the filter network established by C2 and R2. The fast charge and slow discharge rate of C2 establishes a steady 1 on Pin 1 of GlA even though the output of GlB is pulsing. Thus, in but cases, a steady 0 appears on Pin 3 of GlA. The O then on the lase of Q1 allows the collector of Q2 becomes a 0. If the key is connected to a keyer with a negative ground the O would pass through D2 and place a O on the positive voltage of the keyer's imput circuit. If the key is connected to a keyer with a positive ground D2 would be ineffective. However, the O at the collector of Q2 passes through D3 and places a O on the negative

SINGLE KEY OPERATION is the same as that discussed above under Twin Key Operation with the folioning exceptions: When the key operates in the Twin Key mode, a steady 1 is applied to Pin 2 of GIA and Pin 13 of GID. This voltage allows these two gates to function independently of one another. When the key is strapped to operate in the Single Key mode, the output of GIA is fed to one input of GID and the output of GID is fed to one input of GIA. This latching arrangement prevents an output from either gate if a previous gate is activated. That is, if the DASH paddle is touched, Pin 11 of GID will be at a 0, this 0 via strap C and E is applied to

## Courtesy of the N7CFO archives. WWW.N7CFO.COM

## Courtesy of the N7CFO archives. WWW.N7CFO.COM

Pin 2 of GlA. If the DOT paddle is now touched, Pin 3 of GlA remains at a 1, even when Pin 1 goes to a 1, due to the 0 on Pin 2 from GlD. The DOT output thus is prevented, and will be until the DASH paddle is released and the 1 restored to Pin 2 of GlA.

OUTPUT of each key paddle is through two diode protected open transistor collectors, an NPN and PNP. The PNP transistor functions when the key is used with a positive ground keyer and is capable of keying up to negative 20 volts at 20 mA. The NPN transistor functions when the key is used with a negative ground key and is capable of keying up to positive 12 volts at 20 mA. If the key is used to drive an inductive load, voltage spikes developed by the inductive load must be suppressed. Failure to provide suitable suppression will permanently damage the output transistor drivers.

INTERNAL KEY STRAPS on the printed circuit board allow the user a choice between a Single Paddle or Twin Paddle Key. Unless otherwise requested, the key comes from the plant strapped to function as a Twin Paddle Key, that is, a strap between terminals A-B and E-F. To convert to a Single Paddle Key, strap terminals B to D and C to E.

The Option available with the key provides two single pole double throw push button switches. The switches are used for manual starting and stopping of memory messages in the Data Engineering, Inc. Memory-Matic Keyers, or can be connected as a remote TUNE switch, etc.

KEY CONNECTION: The standard key is equipped with a two-wire shielded cable, while the key with option has a four-wire shielded cable. The color-coded conductors of the calle and their use is shown in the schematic diagra. In both cases, the shield serves as the ground between ker and agger. The Red ire in the cable is connected to the DASH input. (The red and black lires can be reversed if left-handed operation is desired.) In those keys with the option, the Red button is connected to the Green wire in the cable and in turn should be connected to Pin 2 of the five-prong plug provided with the Data Engineering, Inc. Memory-Matic Keyers. The Black button is connected to the White wire and should be connected to pin 4 of the same five-prong plug.

<u>RF IMMUNITY</u> is provided by the use of shielded cable. Additional suppression is provided by the use of by-pass capacitors on each cable conductor and paddle. If required, by-pass capacitors should be added to the terminated end of each cable conductor.

ERRATIC KEYING: The input of the key is by a physical touch of the twin paddles. The touch of a puddle reduces the input voltage of the COS-MOS NAND gates sufficiently, to cause their conduction.

If the voltage is not reduced sufficiently to cause adequate conduction, erratic keying will result. This condition, however, can be corrected by reversing the AC power plug to the key.

NOTE: The new paddle design with adjacent grids, requires touching of two of the adjacent grids simultaneously for proper keying operation.